- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

- Conseil de base

- Conseil industriel

- Carte de transport de kit de développement

- Carte porteuse du kit de développement PX30

- Carte porteuse du kit de développement RK3399

- Carte porteuse du kit de développement RV1126

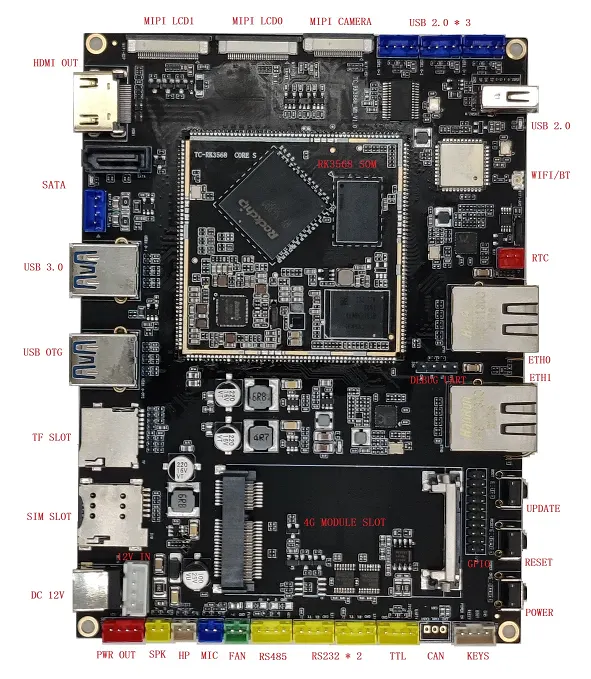

- Carte porteuse du kit de développement RK3568

- Carte de support du kit de développement RK3566

- Carte de support du kit de développement RK3588

- RK3562 Board de transporteur de kit de développement

- Ordinateur embarqué

- Accessoires

- Verrouillage intelligent

- Ordinateur à carte unique

- Tu as peu

Carte de développement RK3568

RK3568, le processeur Cortex-A55 quadricœur 64 bits, avec processus de lithographie 22 nm, a une fréquence allant jusqu'à 2,0 GHz, offrant des performances efficaces et stables pour le traitement des données des équipements back-end. Il existe une variété d'options de stockage, permettant aux clients de mettre en œuvre rapidement la recherche et la production de produits. Il prend en charge jusqu'à 8 Go de RAM, avec jusqu'à 32 bits de largeur et une fréquence jusqu'à 1600 MHz. Il prend en charge l'ECC toutes liaisons de données, ce qui rend les données plus sûres et plus fiables et répond aux exigences de l'exécution d'applications de produits à grande mémoire. Il est intégré avec un GPU double cœur, un VPU haute performance et un NPU haute efficacité. Le GPU prend en charge OpenGL ES3.2/2.0/1.1, Vulkan1.1. Le VPU peut réaliser un décodage vidéo 4K 60fps H.265/H.264/VP9 et un encodage vidéo 1080P 100fps H.265/H.264. Le NPU prend en charge la commutation en un clic des frameworks traditionnels tels que Caffe/TensorFlow.

envoyer une demande Téléchargement PDF

Spécification de la carte de développement Thinkcore TC-RK3568 Stamp Hole

Déclaration de droit d'auteur

Les droits d'auteur de ce manuel appartiennent à Shenzhen Thinkcore Technology Co., Ltd. et tous les droits sont réservés. Aucune entreprise ou personne n'est autorisée à extraire une partie ou la totalité de ce manuel, et les contrevenants seront poursuivis en vertu de la loi.

Attention:

Les manuels de la plate-forme de développement en vente seront mis à jour de temps à autre, veuillez télécharger le dernier manuel sur le site Web www.think-core.com ou contacter notre représentant commercial de l'entreprise, il n'y aura pas d'autre avis.

Note de version

|

Version |

Date |

Auteur |

La description |

|

Rév.01 |

2022-08-04 |

|

Révision |

Chapitre 1. Présentation de la carte de développement TC-RK3568 Stamp Hole

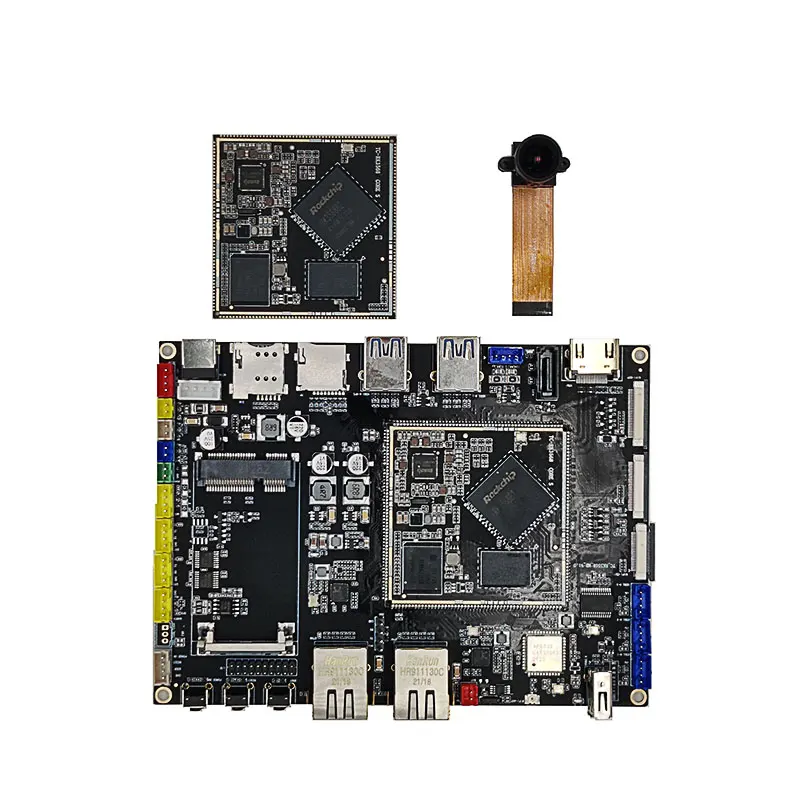

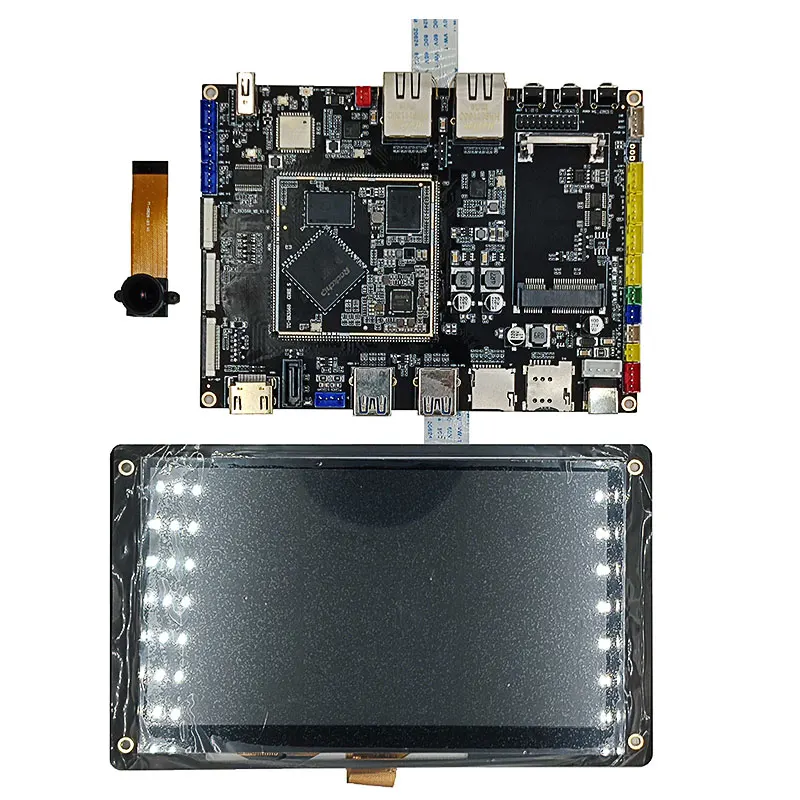

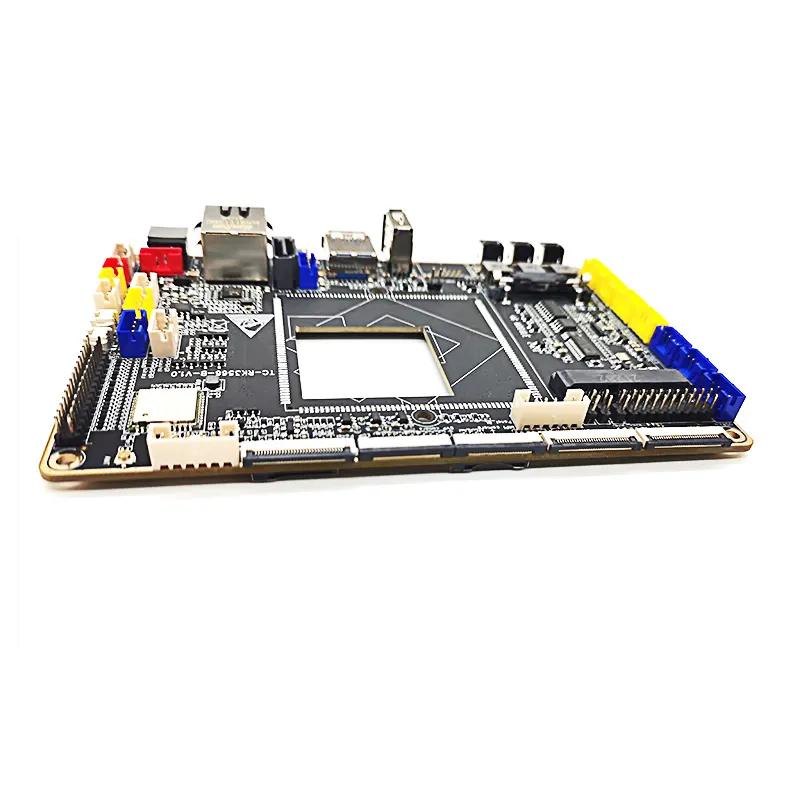

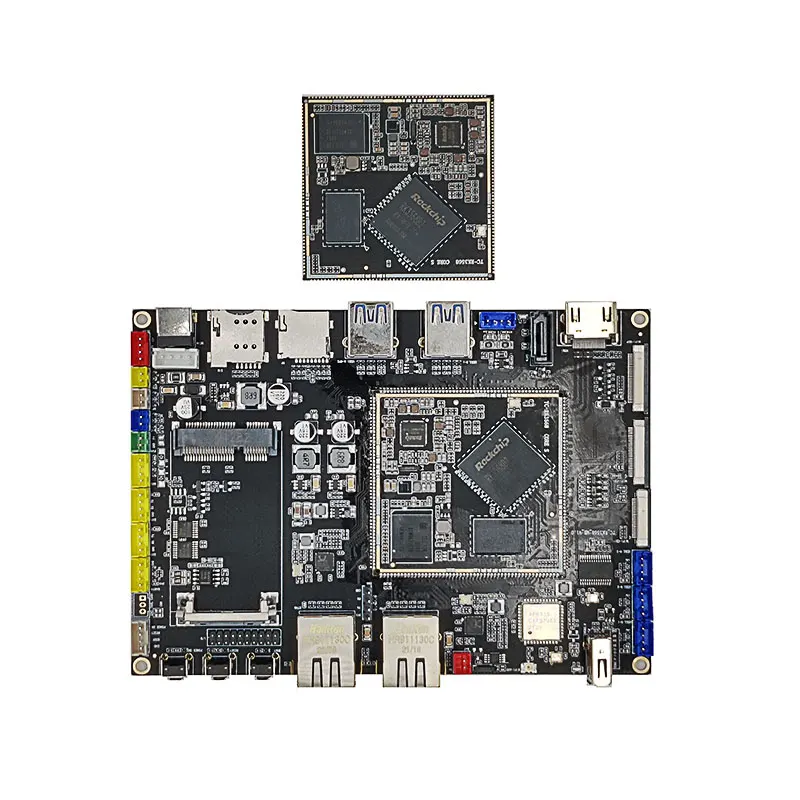

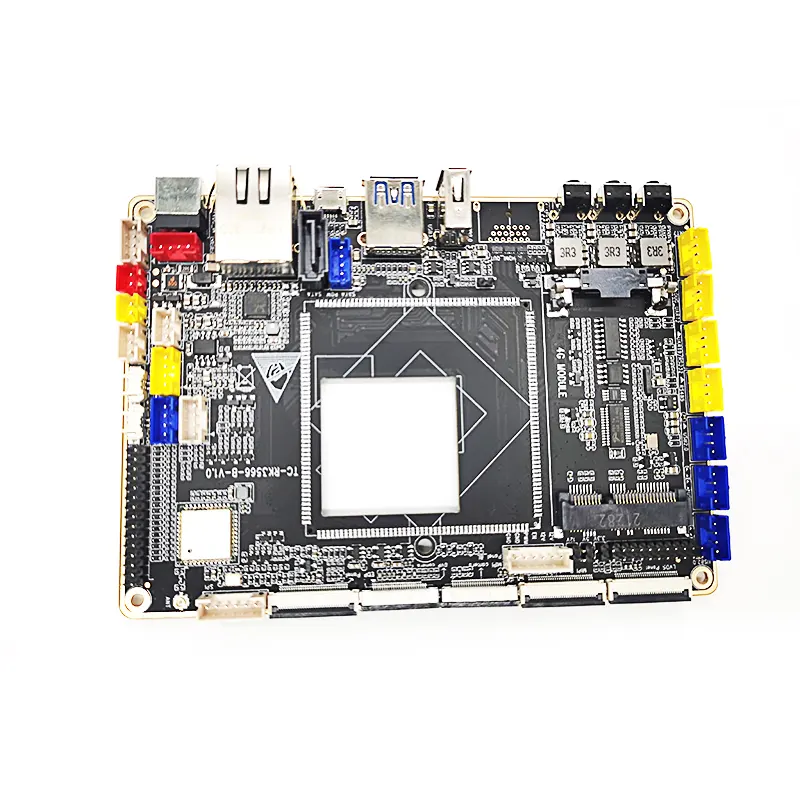

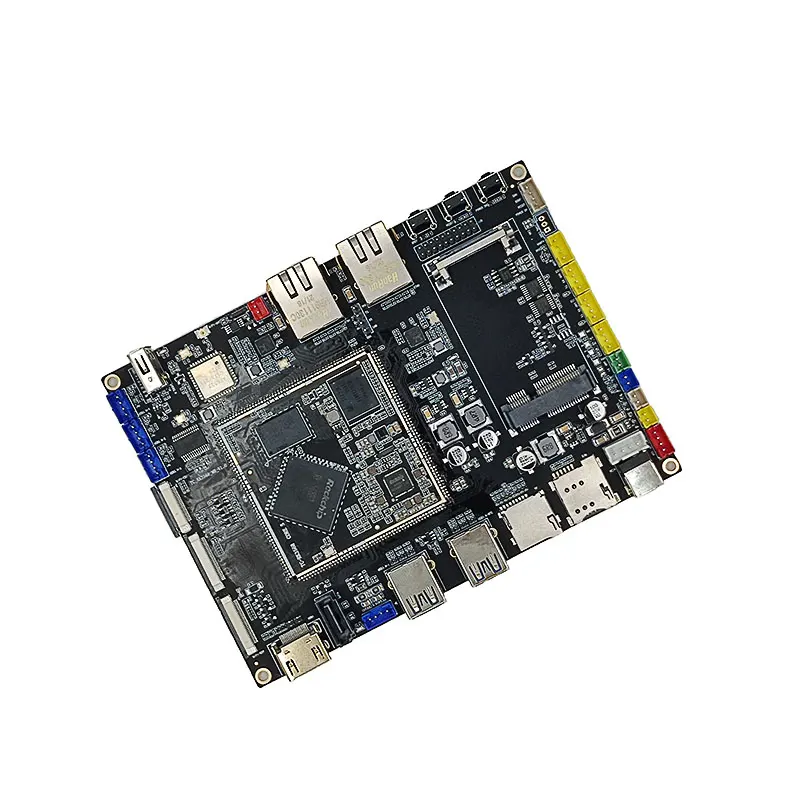

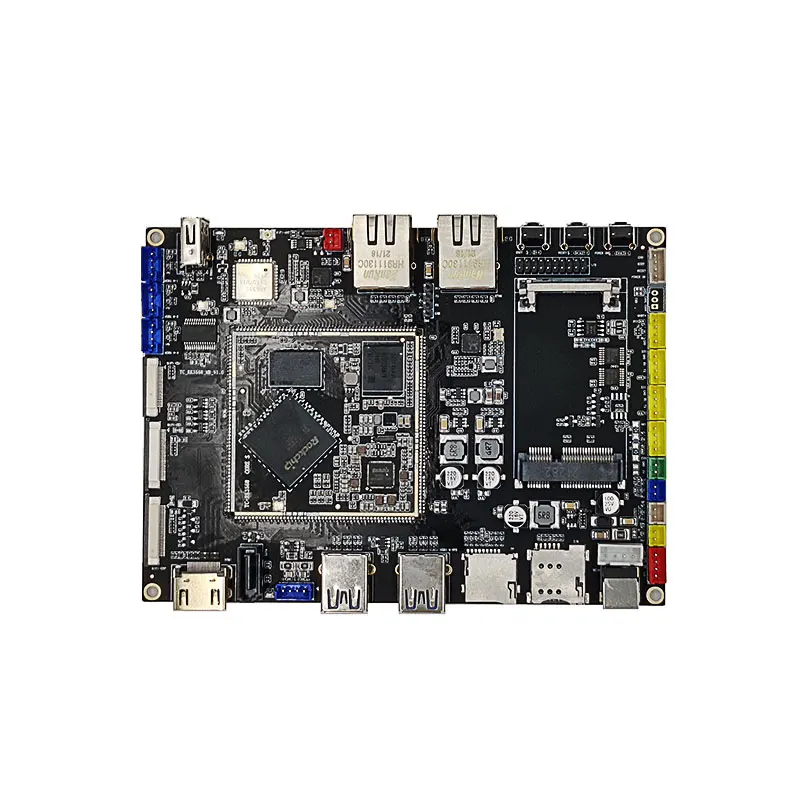

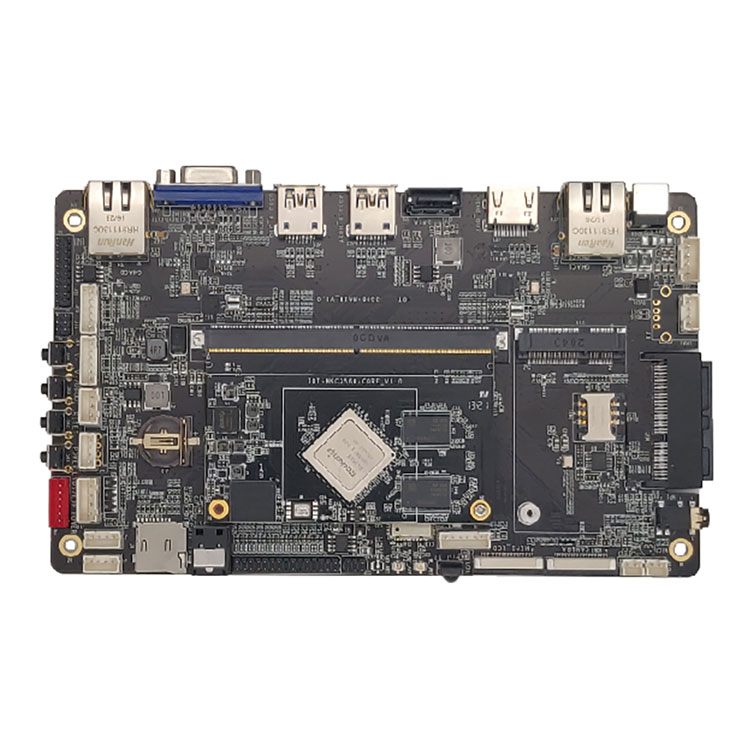

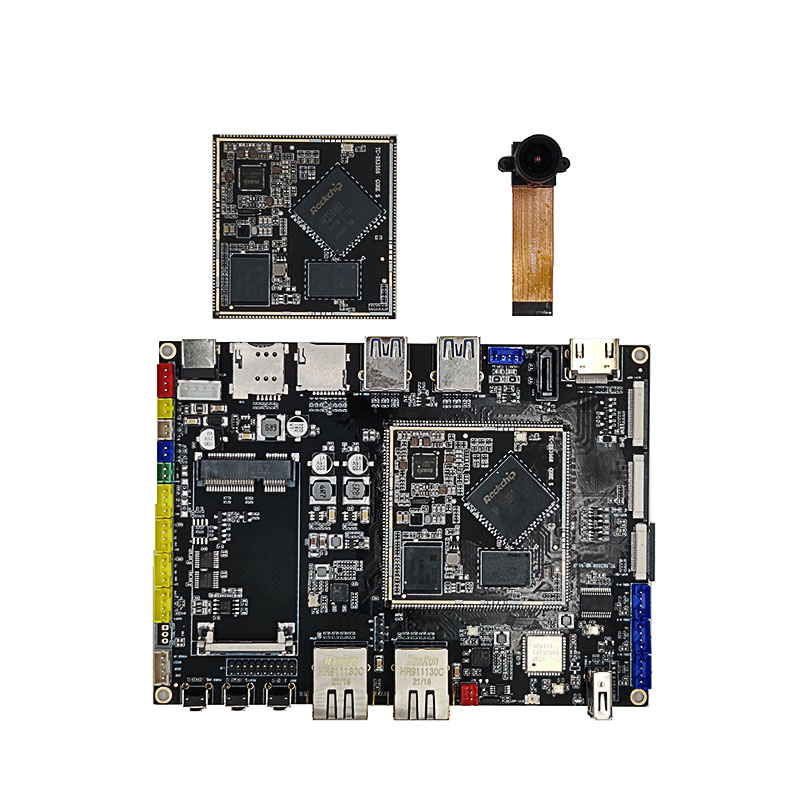

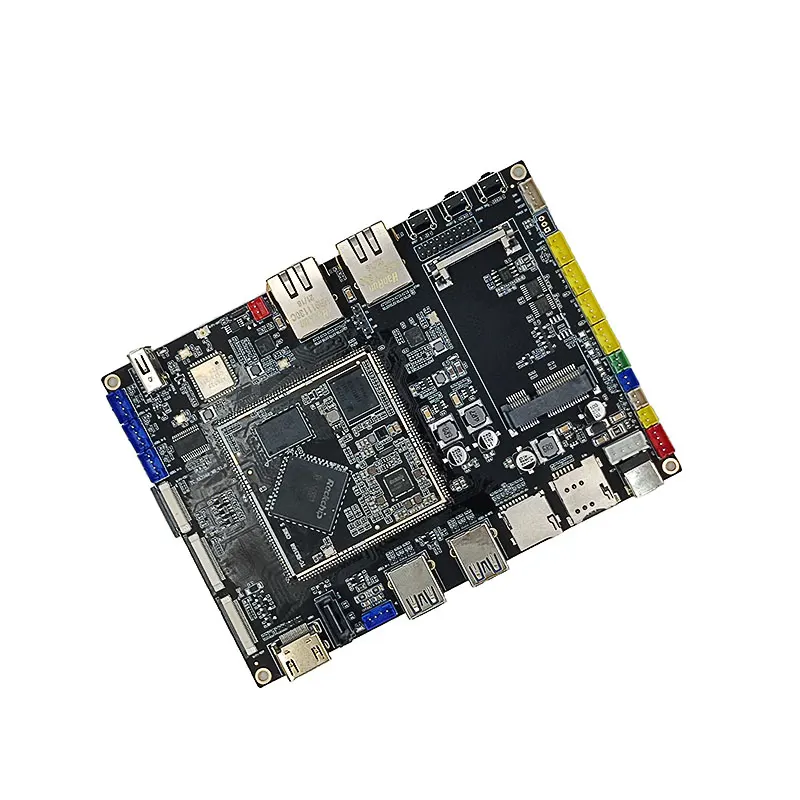

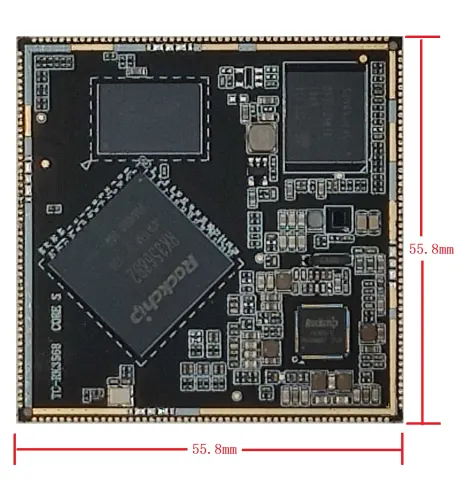

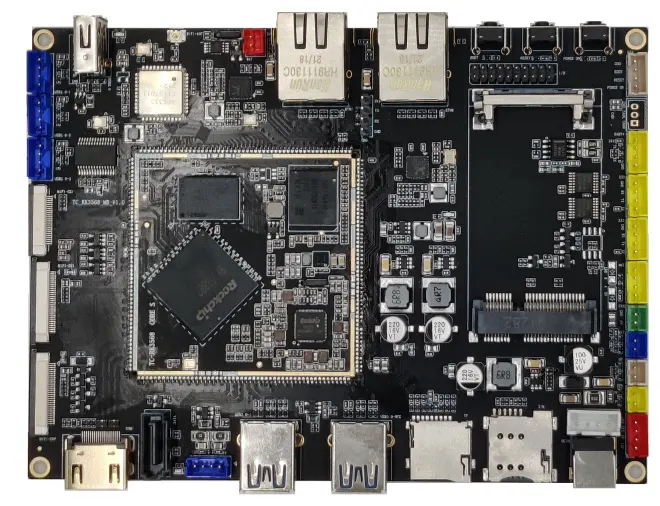

TC-RK3568 Fiche de la carte de développement Stamp Hole

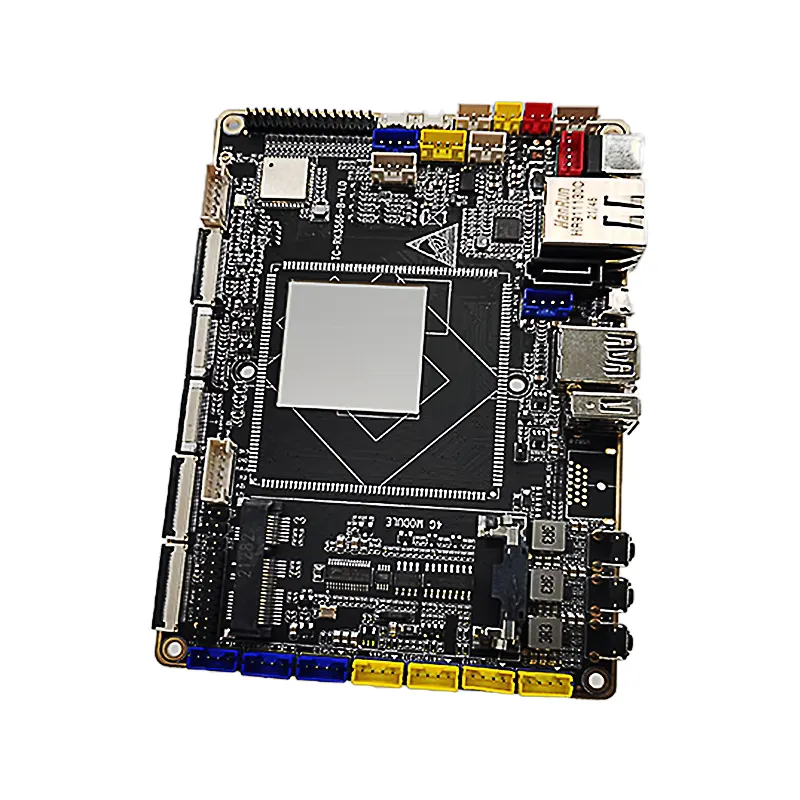

La carte de développement de trou de tampon TC-RK3568 comprend un SOM de trou de tampon TC-RK3568 et une carte de support.

Le système TC-RK3568 Stamp Hole sur module est équipé d'un processeur Rockchip 64 bits RK3568 qui est configuré avec un GPU double cœur et un NPU haute performance.

RK3568, le processeur Cortex-A55 quadricœur 64 bits, avec processus de lithographie 22 nm, a une fréquence allant jusqu'à 2,0 GHz, offrant des performances efficaces et stables pour le traitement des données des équipements back-end. Il existe une variété d'options de stockage, permettant aux clients de mettre en œuvre rapidement la recherche et la production de produits. Il prend en charge jusqu'à 8 Go de RAM, avec jusqu'à 32 bits de largeur et une fréquence jusqu'à 1600 MHz. Il prend en charge l'ECC toutes liaisons de données, ce qui rend les données plus sûres et plus fiables et répond aux exigences de l'exécution d'applications de produits à grande mémoire. Il est intégré avec un GPU double cœur, un VPU haute performance et un NPU haute efficacité. Le GPU prend en charge OpenGL ES3.2/2.0/1.1, Vulkan1.1. Le VPU peut réaliser un décodage vidéo 4K 60fps H.265/H.264/VP9 et un encodage vidéo 1080P 100fps H.265/H.264. Le NPU prend en charge la commutation en un clic des frameworks traditionnels tels que Caffe/TensorFlow.

Avec les interfaces vidéo MIPI-CSI x2, MIPI-DSI x2, HDMI2.0, EDP, il peut prendre en charge jusqu'à trois sorties d'écran avec un affichage différent. Le FAI 8M intégré prend en charge les caméras doubles et HDR. L'interface d'entrée vidéo peut être connectée à une caméra externe ou à plusieurs caméras. Il est équipé de deux ports Ethernet Gigabit RJ45 adaptatifs, à travers lesquels les données réseau internes et externes peuvent être consultées et transmises, améliorant l'efficacité de la transmission réseau et répondant aux besoins des produits avec plusieurs ports réseau tels que NVR et passerelle industrielle.

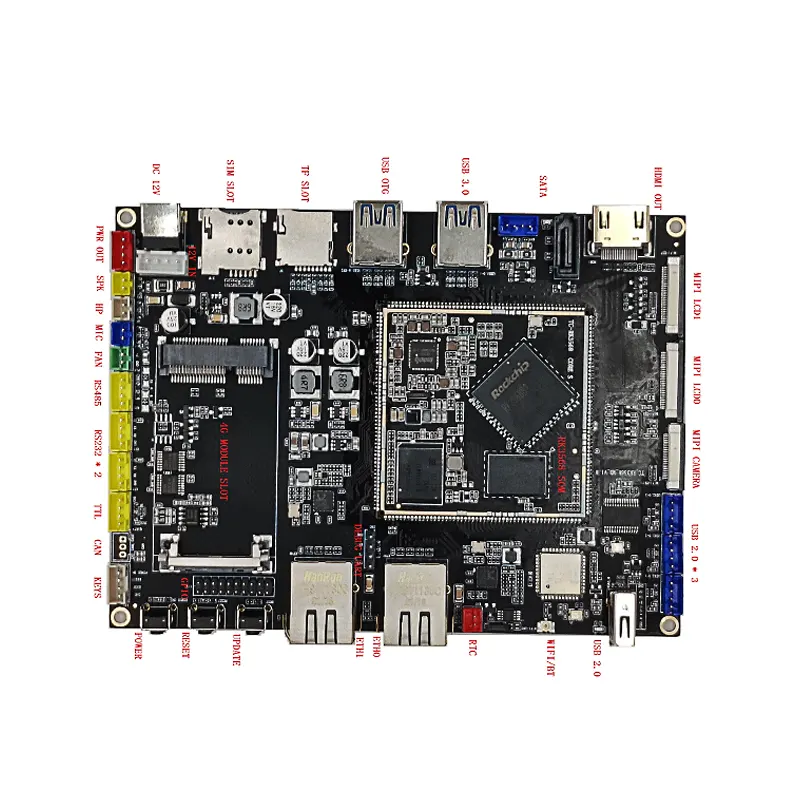

La carte porteuse comprend de nombreuses interfaces, telles que le port 4G LTE, USB3.0, USB2.0, PCIE, double Ethernet, WIFI, Bluetooth, entrée et sortie audio, sortie HDMI, affichage MIPI DSI, affichage eDP, affichage LVDS, MIPI CSI caméra, emplacement pour carte TF, RS485, RS232, TTL, CAN, Power out, SATA, etc.

Android 11, Ubuntu 18.04 OS, Debian OS et Linux Buildroot sont pris en charge. Le fonctionnement stable et fiable fournit un environnement système sûr et stable pour la recherche et la production de produits.

Un SDK complet, des documents de développement, des exemples, des documents technologiques, des tutoriels et d'autres ressources sont fournis aux utilisateurs pour une personnalisation plus poussée.

Caractéristiques de la carte de développement de trou de tampon TC-RK3568 :

Taille : 150 mm x 110 mm.

Des interfaces riches, peuvent être directement utilisées dans divers produits intelligents pour faciliter la réalisation des produits.

Android 11.0, Ubuntu 18.04 OS, Debian OS et Linux Buildroot sont pris en charge.

Application

Cette carte peut être largement utilisée dans les NVR intelligents, les terminaux cloud, les passerelles IoT, le contrôle industriel, l'informatique de pointe, les portes de reconnaissance faciale, les NAS, les consoles centrales des véhicules, etc.

Paramètre caractéristique

|

Caractéristiques |

|

|

CPU |

RockChip RK3568, Quad-core 64 bits Cortex-A55, processus de lithographie 22 nm, fréquence jusqu'à 2,0 GHz |

|

GPU |

BRAS G52 2EE Prend en charge OpenGL ES 1.1/2.0/3.2, OpenCL 2.0, Vulkan 1.1 Matériel d'accélération 2D hautes performances intégré |

|

NPU |

0.8Tops@INT8, accélérateur d'IA haute performance intégré RKNN NPU Prend en charge la commutation en un clic de Caffe/TensorFlow/TFLite/ONNX/PyTorch/Keras/Darknet |

|

VPU |

Prend en charge le décodage vidéo 4K 60fps H.265/H.264/VP9 Prend en charge l'encodage vidéo 1080P 100fps H.265/H.264 Prend en charge 8M ISP, prend en charge HDR |

|

RAM |

2 Go/4 Go/8 Go |

|

Stockage |

8 Go/16 Go/32 Go/64 Go/128 Go eMMC Prend en charge SATA 3.0 x 1 (extension avec 2,5" SSD/HDD) Prend en charge l'emplacement pour carte TF x1 (développez avec la carte TF) |

|

Système d'exploitation |

Android11/Linux Buildroot/Ubuntu/Debian |

|

Caractéristiques matérielles |

|

|

Afficher |

1 * HDMI2.0, prend en charge la sortie 4K @ 60fps 1 * MIPI DSI, prend en charge la sortie 1920*1080 @ 60fps 1 * LVDS, prend en charge la sortie 1920*1080 @ 60fps 1 * eDP1.3, prend en charge la sortie 2560x1600 @ 60fps |

|

Ethernet |

Prend en charge deux ports Ethernet Gigabit (1000 Mbps) |

|

Wifi |

Mini PCIe pour connecter la 4G LTE Prend en charge le Wi-Fi 6 (802.11 AX) Prend en charge BT5.0 |

|

PCIE3.0 |

Prend en charge l'interface PCE3.0 |

|

l'audio |

1 * sortie audio HDMI 1 * sortie haut-parleur 1 * Sortie écouteurs 1 * entrée audio intégrée au microphone |

|

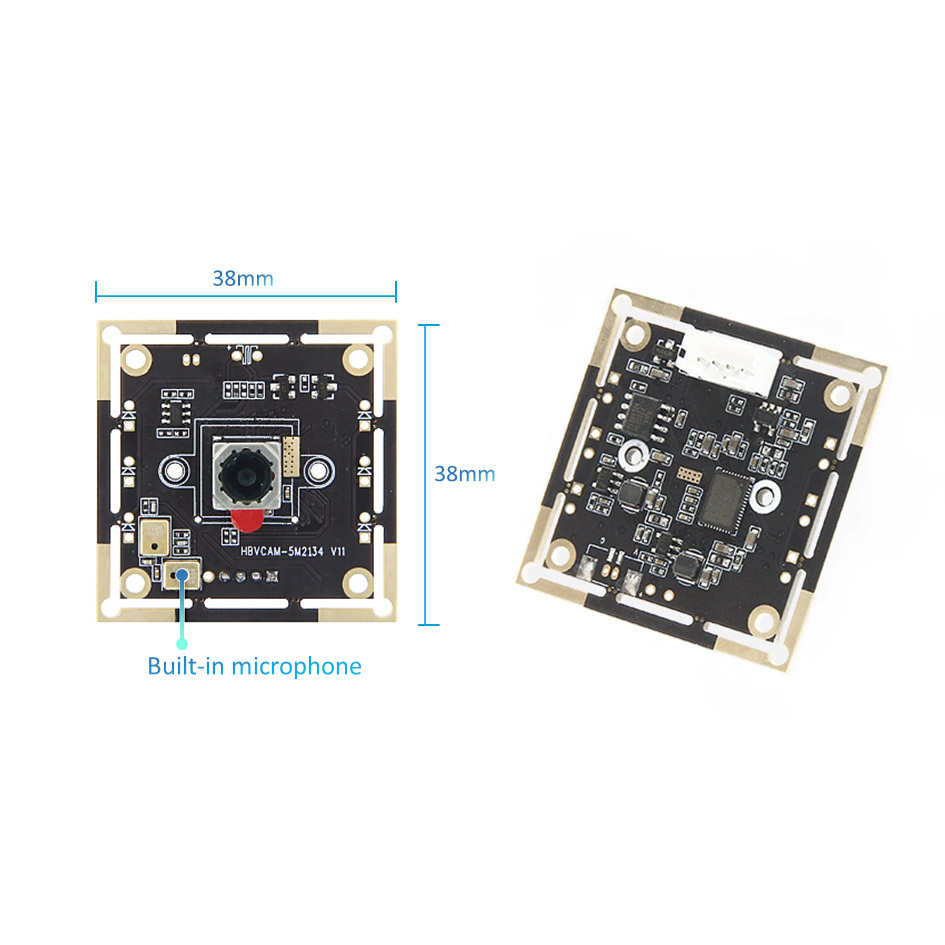

Appareil photo |

Prend en charge l'interface de caméra MIPI-CSI à 1 canal Prend en charge le HDR, l'image reste claire en contre-jour ou dans des conditions de forte luminosité

|

|

USB |

1 * hôte USB3.0, 4 * hôte USB 2.0, 1 * USB3.0 OTG |

|

SATA |

1 * SATA, 6,0 Go/s |

|

En série |

1 * TTL, 2 * RS232, 1 * RS485 |

|

POUVEZ |

Prend en charge CAN2.0B, prend en charge 1 Mbps, 8 Mbps |

|

Carte TF |

1 * emplacement pour carte TF |

|

Autres |

GPIO et ADC |

|

Taille |

150mm*110mm |

|

|

|

|

Tension d'entrée |

12V/3A |

|

Température de stockage

|

-30~80â |

|

Température de fonctionnement |

-20~60â |

|

Humidité de stockage |

10 % ~ 80 % |

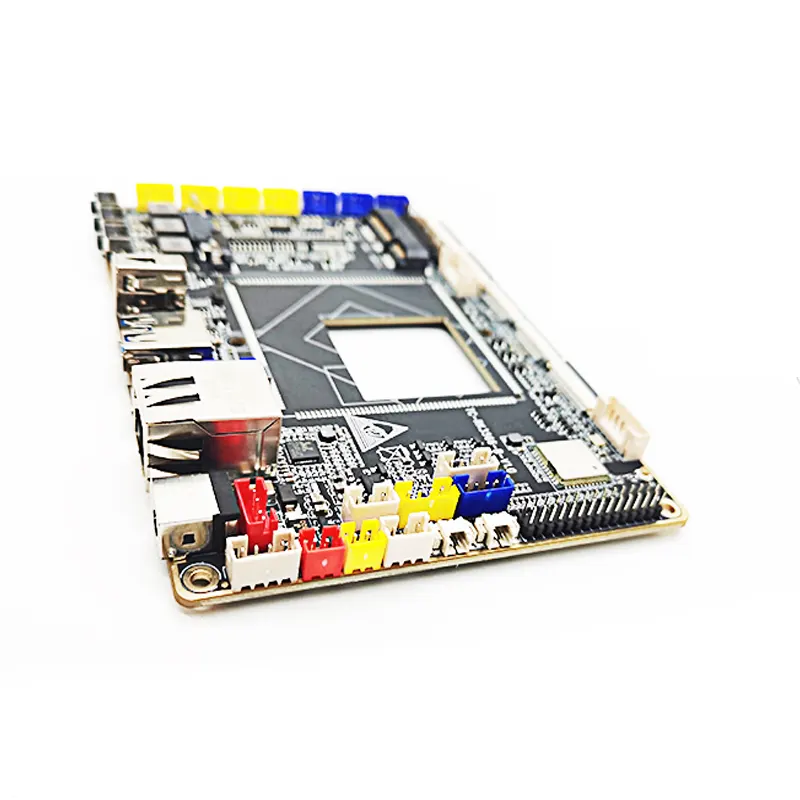

Apparence SOM

Avant SOM

Apparition au conseil de développement

Chapitre 2. Définition du PIN SOM

Définition du code PIN SOM

|

ÉPINGLER |

Définition des broches de la carte mère |

Fonction par défaut |

Description de la fonction par défaut |

Puissance E/S |

Type de tampon IO pull |

|

1 |

VCC3V3_SYS |

Alimentation du système 3.3V |

Tension d'entrée 3.3V |

|

- |

|

2 |

VCC3V3_SYS |

Alimentation du système 3.3V |

Tension d'entrée 3.3V |

|

- |

|

3 |

Terre |

Terre |

Terre |

|

- |

|

4 |

Terre |

Terre |

Terre |

|

- |

|

5 |

SDMMC0_DET_L |

SDMMC0_DET/SATA_CP_DET/PCIE30X1_CLKREQn_M0/GPIO0_A4_u |

Entrée de détection SDMMC0 |

3.3V |

E/S HAUT |

|

6 |

SDMMC0_D3 |

SDMMC0_D3/ARMJTAG_TMS/UART5_RTSn_M0/GPIO2_A0_u |

Port de données SDMMC0 |

3.3V |

E/S HAUT

|

|

7 |

SDMMC0_D2 |

SDMMC0_D2/ARMJTAG_TCK/UART5_CTSn_M0/GPIO1_D7_u |

Port de données SDMMC0 |

3.3V |

E/S HAUT

|

|

8 |

SDMMC0_D1 |

SDMMC0_D1/UART2_RX_M1/UART6_RX_M1/PWM9_M1/GPIO1_D6_u |

Port de données SDMMC0 |

3.3V |

E/S HAUT

|

|

9 |

SDMMC0_D0 |

SDMMC0_D0/UART2_TX_M1/UART6_TX_M1/PWM8_M1/GPIO1_D5_u |

Port de données SDMMC0 |

3.3V |

E/S HAUT

|

|

10 |

SDMMC0_CMD |

SDMMC0_CMD/PWM10_M1/UART5_RX_M0/CAN0_TX_M1/GPIO2_A1_u |

Sortie de commande SDMMC0 |

3.3V |

E/S HAUT

|

|

11 |

SDMMC0_CLK |

SDMMC0_CLK/TEST_CLKOUT/UART5_TX_M0/CAN0_RX_M1/GPIO2_A2_d |

Sortie d'horloge SDMMC0

|

3.3V |

E/S BAS |

|

12 |

RÉINITIALISER |

NPOR_U |

Détection du signal de réinitialisation |

3.3V |

- |

|

13 |

RK809_PWRON |

Allumer |

Entrée de signal de mise sous tension, touche d'alimentation de connexion externe, actif bas |

|

- |

|

14 |

RÉCUPÉRATION |

SARADC_VIN0 |

Entrée clavier AD |

1.8V |

- |

|

15 |

EXT_FR |

EXT_FR |

Activation de l'alimentation PMIC |

|

- |

|

16 |

HPR_OUT |

HPR_OUT |

Casque tout droit sorti |

3.3V |

- |

|

17 |

HPL_OUT |

HPL_OUT |

Casque laissé de côté |

3.3V |

- |

|

18 |

SPKP_OUT |

SPKP_OUT |

S'exprimer |

5V/0.6W |

- |

|

19 |

SPKN_OUT |

SPKN_OUT |

S'exprimer- |

5V/0.6W |

- |

|

20 |

MIC1_INN |

MIC1_INN/MIC_R |

MIC1_INN |

3.3V |

- |

|

21 |

MIC1_INP |

MIC1_INP/MIC_L |

MIC1_INP |

3.3V |

- |

|

22 |

HP_DET_L_GPIO3_C2 |

LCDC_VSYNC/VOP_BT1120_D14/SPI1_MISO_M1/UART5_TX_M1/I2S1_SDO3_M2/GPIO3_C2_d |

Casque détecter |

3.3V |

E/S BAS |

|

23 |

SPK_CTL_H_GPIO3_C3 |

LCDC_DEN/VOP_BT1120_D15/SPI1_CLK_M1/UART5_RX_M1/I2S1_SCLK_RX_M2/GPIO3_C3_d |

|

3.3V |

E/S BAS |

|

24 |

VCC3V3_SD |

Alimentation 3.3V |

Tension de sortie 3.3V pour carte SD, courant de sortie nominal 2A |

|

- |

|

25 |

VCC_3V3 |

Alimentation 3.3V |

Tension de sortie 3,3 V, courant de sortie nominal 2 A |

|

- |

|

26 |

VCC_1V8 |

Alimentation 1.8V |

Tension de sortie 1,8 V, courant de sortie nominal 2,5 A |

|

- |

|

27 |

PDM_SDI1_M0_ADC |

I2S1_SDO3_M0/I2S1_SDI1_M0/PDM_SDI1_M0/PCIE20_PERSTn_M2/GPIO1_B2_d |

PDM_SDI1_M0_ADC |

3.3V |

E/S BAS |

|

28 |

PDM_SDI2_M0_ADC |

I2S1_SDO2_M0/I2S1_SDI2_M0/PDM_SDI2_M0/PCIE20_WAKEn_M2/ACODEC_ADC_SYNC/GPIO1_B1_d |

PDM_SDI2_M0_ADC |

3.3V |

E/S BAS |

|

29 |

PDM_SDI3_M0_ADC |

I2S1_SDO1_M0/I2S1_SDI3_M0/PDM_SDI3_M0/PCIE20_CLKREQn_M2/ACODEC_DAC_DATAR/GPIO1_B0_d |

PDM_SDI3_M0_ADC |

3.3V |

E/S BAS |

|

30 |

PDM_CLK1_M0_ADC |

I2S1_SCLK_RX_M0/UART4_RX_M0/PDM_CLK1_M0/SPDIF_TX_M0/GPIO1_A4_d |

PDM_CLK1_M0_ADC |

3.3V |

E/S BAS |

|

31 |

GMAC0_TXD0 |

GMAC0_TXD0/UART1_RX_M0/GPIO2_B3_u |

GMAC0 transmet des données |

1.8V |

E/S HAUT |

|

32 |

GMAC0_TXD1 |

GMAC0_TXD1/UART1_TX_M0/GPIO2_B4_u |

GMAC0 transmet des données |

1.8V |

E/S HAUT |

|

33 |

GMAC0_TXD2 |

SDMMC1_D3/GMAC0_TXD2/UART7_TX_M0/GPIO2_A6_u |

GMAC0 transmet des données |

1.8V |

E/S HAUT |

|

34 |

GMAC0_TXD3 |

SDMMC1_CMD/GMAC0_TXD3/UART9_RX_M0/GPIO2_A7_u |

GMAC0 transmet des données |

1.8V |

E/S HAUT |

|

35 |

GMAC0_TXFR |

GMAC0_TXEN/UART1_RTSn_M0/SPI1_CLK_M0/GPIO2_B5_u |

Activation de la transmission GMAC0 |

1.8V |

E/S HAUT |

|

36 |

GMAC0_TXCLK |

SDMMC1_CLK/GMAC0_TXCLK/UART9_TX_M0/GPIO2_B0_d |

Horloge de transmission GMAC0 |

1.8V |

E/S BAS |

|

37 |

GMAC0_RXD0 |

GMAC0_RXD0/UART1_CTSn_M0/SPI1_MISO_M0/GPIO2_B6_u |

GMAC0 reçoit des données |

1.8v |

E/S HAUT |

|

38 |

GMAC0_RXD1 |

I2S2_SCLK_RX_M0/GMAC0_RXD1/UART6_RTSn_M0/SPI1_MOSI_M0/GPIO2_B7_d |

GMAC0 reçoit des données |

1.8V |

E/S BAS |

|

39 |

GMAC0_RXD2 |

SDMMC1_D0/GMAC0_RXD2/UART6_RX_M0/GPIO2_A3_u |

GMAC0 reçoit des données |

1.8v |

E/S HAUT |

|

40 |

GMAC0_RXD3 |

SDMMC1_D1/GMAC0_RXD3/UART6_TX_M0/GPIO2_A4_u |

GMAC0 reçoit des données |

1.8V |

E/S HAUT |

|

41 |

GMAC0_RXDV_CRS |

I2S2_LRCK_RX_M0/GMAC0_RXDV_CRS/UART6_CTSn_M0/SPI1_CS0_M0/GPIO2_C0_d |

Signal valide de données GMAC0 RX |

1.8V |

E/S BAS |

|

42 |

GMAC0_RXCLK |

SDMMC1_D2/GMAC0_RXCLK/UART7_RX_M0/GPIO2_A5_u |

Horloge de réception GMAC0 |

1.8V |

E/S HAUT |

|

43 |

ETH0_REFCLKO_25M |

I2S2_MCLK_M0/ETH0_REFCLKO_25M/UART7_RTSn_M0/SPI2_CLK_M0/GPIO2_C1_d |

ETH0_REF CLOCK OUTPUT_25MHz CPU vers PHY, NC par défaut |

1.8V |

E/S BAS |

|

44 |

GMAC0_MCLKINOUT |

I2S2_SCLK_TX_M0/GMAC0_MCLKINOUT/UART7_CTSn_M0/SPI2_MISO_M0/GPIO2_C2_d |

Horloge externe GMAC0 |

1.8V |

E/S BAS |

|

45 |

GMAC0_MDC |

I2S2_LRCK_TX_M0/GMAC0_MDC/UART9_RTSn_M0/SPI2_MOSI_M0/GPIO2_C3_d |

Horloge de gestion MAC0 |

1.8V |

E/S BAS |

|

46 |

GMAC0_MDIO |

I2S2_SDO_M0/GMAC0_MDIO/UART9_CTSn_M0/SPI2_CS0_M0/GPIO2_C4_d |

Commande et données de gestion MAC0 |

1.8V |

E/S BAS |

|

47 |

GMAC0_RSTN_GPIO3_B7 |

LCDC_D21/VOP_BT1120_D12/GMAC1_TXD1_M0/I2C3_SDA_M1/PWM11_IR_M0/GPIO3_B6_d |

|

3.3V |

E/S BAS |

|

48 |

GMAC0_INT_PMEB_GPIO3_C0 |

LCDC_HSYNC/VOP_BT1120_D13/SPI1_MOSI_M1/PCIE20_PERSTn_M1/I2S1_SDO2_M2/GPIO3_C1_d |

|

3.3V |

E/S BAS |

|

49 |

RTCTC_INT_L_GPIO0_D3 |

GPIO0_D3_d |

RTC_IC_INT, actif bas |

1.8V |

E/S BAS |

|

50 |

I2C5_SDA_M0 |

LCDC_D19/VOP_BT1120_D10/GMAC1_RXER_M0/I2C5_SDA_M0/PDM_SDI1_M2/GPIO3_B4_d |

Port série I2C 5 |

3.3V |

E/S BAS |

|

51 |

I2C5_SCL_M0 |

LCDC_D18/VOP_BT1120_D9/GMAC1_RXDV_CRS_M0/I2C5_SCL_M0/PDM_SDI0_M2/GPIO3_B3_d |

Port série I2C 5 |

3.3V |

E/S BAS |

|

52 |

PWM3_IR |

PWM3_IR/EDP_HPDIN_M1/PCIE30X1_WAKEn_M0/MCU_JTAG_TMS/GPIO0_C2_d |

|

3.3V |

E/S BAS |

|

53 |

CAN1_TX_M1 |

PWM15_IR_M1/SPI3_MOSI_M1/CAN1_TX_M1/PCIE30X2_WAKEn_M2/I2S3_SCLK_M1/GPIO4_C3_d |

Transmission de données PEUT |

3.3V |

E/S BAS |

|

54 |

CAN1_RX_M1 |

PWM14_M1/SPI3_CLK_M1/CAN1_RX_M1/PCIE30X2_CLKREQn_M2/I2S3_MCLK_M1/GPIO4_C2_d |

Réception de données CAN |

3.3V |

E/S BAS |

|

55 |

UART2_RX_M0_DEBUG |

UART2_RX_M0/GPIO0_D0_u |

Port série UART |

3.3V |

E/S HAUT |

|

56 |

UART2_TX_M0_DEBUG |

UART2_TX_M0/GPIO0_D1_u |

Transmission de données de port série UART pour le débogage |

3.3V |

E/S HAUT |

|

57 |

UART3_RX_M1 |

LCDC_D23/PWM13_M0/GMAC1_MCLKINOUT_M0/UART3_RX_M1/PDM_SDI3_M2/GPIO3_C0_d |

Réception de données de port maritime UART |

3.3V |

E/S BAS |

|

58 |

UART3_TX_M1 |

LCDC_D22/PWM12_M0/GMAC1_TXEN_M0/UART3_TX_M1/PDM_SDI2_M2/GPIO3_B7_d |

Transmission de données de port maritime UART |

3.3V |

E/S BAS |

|

59 |

UART4_TX_M1 |

LCDC_D17/VOP_BT1120_D8/GMAC1_RXD1_M0/UART4_TX_M1/PWM9_M0/GPIO3_B2_d |

Transmission de données de port maritime UART |

3.3V |

E/S BAS |

|

60 |

UART4_RX_M1 |

LCDC_D16/VOP_BT1120_D7/GMAC1_RXD0_M0/UART4_RX_M1/PWM8_M0/GPIO3_B1_d |

Réception de données de port maritime UART |

3.3V |

E/S BAS |

|

61 |

UART9_RX_M1 |

PWM13_M1/SPI3_CS0_M1/SATA0_ACT_LED/UART9_RX_M1/I2S3_SDI_M1/GPIO4_C6_d |

Réception de données de port maritime UART |

3.3V |

E/S BAS |

|

62 |

UART9_TX_M1 |

PWM12_M1/SPI3_MISO_M1/SATA1_ACT_LED/UART9_TX_M1/I2S3_SDO_M1/GPIO4_C5_d |

Transmission de données de port maritime UART |

3.3V |

E/S BAS |

|

63 |

UART7_RX_M1 |

PWM15_IR_M0/SPDIF_TX_M1/GMAC1_MDIO_M0/UART7_RX_M1/I2S1_LRCK_RX_M2/GPIO3_C5_d |

Réception de données de port maritime UART |

3.3V |

E/S BAS |

|

64 |

UART7_TX_M1 |

PWM14_M0/VOP_PWM_M1/GMAC1_MDC_M0/UART7_TX_M1/PDM_CLK1_M2/GPIO3_C4_d |

Transmission de données de port maritime UART |

3.3V |

E/S BAS |

|

65 |

RS485_DIR_GPIO3_B5 |

LCDC_D20/VOP_BT1120_D11/GMAC1_TXD0_M0/I2C3_SCL_M1/PWM10_M0/GPIO3_B5_d |

Direction des données RS485 |

3.3V |

E/S BAS |

|

66 |

DVP_PWREN0_H_GPIO0_B0 |

CLK32K_IN/CLK32K_OUT0/PCIE30X2_BUTTONRSTn/GPIO0_B0_u |

|

3.3V |

E/S HAUT |

|

67 |

WIFI_PWREN_L_GPIO0_C1 |

PWM2_M0/NPUAVS/UART0_TX/MCU_JTAG_TDI/GPIO0_C1_d |

|

3.3V |

E/S BAS |

|

68 |

I2S3_SDI_M0 |

LCDC_D13/VOP_BT1120_CLK/GMAC1_TXCLK_M0/I2S3_SDI_M0/SDMMC2_CLK_M1/GPIO3_A6_d |

I2S3_SDI |

3.3V |

E/S BAS |

|

69 |

I2S3_SDO_M0 |

LCDC_D12/VOP_BT1120_D4/GMAC1_RXD3_M0/I2S3_SDO_M0/SDMMC2_CMD_M1/GPIO3_A5_d |

I2S3_SDO |

3.3V |

E/S BAS |

|

70 |

I2S3_LRCK_M0 |

LCDC_D11/VOP_BT1120_D3/GMAC1_RXD2_M0/I2S3_LRCK_M0/SDMMC2_D3_M1/GPIO3_A4_d |

I2S3_LRCK |

3.3V |

E/S BAS |

|

71 |

I2S3_SCLK_M0 |

LCDC_D10/VOP_BT1120_D2/GMAC1_TXD3_M0/I2S3_SCLK_M0/SDMMC2_D2_M1/GPIO3_A3_d |

I2S3_SCLK |

3.3V |

E/S BAS |

|

72 |

HOST_WAKE_BT_H_GPIO3_A2 |

LCDC_D9/VOP_BT1120_D1/GMAC1_TXD2_M0/I2S3_MCLK_M0/SDMMC2_D1_M1/GPIO3_A2_d |

HOST_WAKE_BT |

3.3V |

E/S BAS |

|

73 |

BT_WAKE_HOST_H_GPIO3_A1 |

LCDC_D8/VOP_BT1120_D0/SPI1_CS0_M1/PCIE30X1_PERSTn_M1/SDMMC2_D0_M1/GPIO3_A1_d |

BT_WAKE_HOST |

3.3V |

E/S BAS |

|

74 |

BT_REG_ON_H_GPIO3_A0 |

LCDC_CLK/VOP_BT656_CLK_M0/SPI2_CLK_M1/UART8_RX_M1/I2S1_SDO1_M2/GPIO3_A0_d |

Activation de l'alimentation du module Bluetooth |

3.3V |

E/S BAS |

|

75 |

UART8_RX_M0 |

CLK32K_OUT1/UART8_RX_M0/SPI1_CS1_M0/GPIO2_C6_d |

Réception de données de port maritime UART |

1,8V |

E/S BAS |

|

76 |

UART8_TX_M0 |

I2S2_SDI_M0/GMAC0_RXER/UART8_TX_M0/SPI2_CS1_M0/GPIO2_C5_d |

Transmission de données de port maritime UART |

1.8V |

E/S BAS |

|

77 |

UART8_CTSN_M0 |

SDMMC1_DET/I2C4_SCL_M1/UART8_CTSn_M0/CAN2_TX_M1/GPIO2_B2_u |

UART8_CTSn_M0 |

1.8V |

E/S BAS |

|

78 |

UART8_RTSN_M0 |

SDMMC1_PWREN/I2C4_SDA_M1/UART8_RTSn_M0/CAN2_RX_M1/GPIO2_B1_d |

UART8_RTSn_M0 |

1.8V |

E/S BAS |

|

79 |

WIFI_REG_ON_H_GPIO3_D5 |

CIF_D7/EBC_SDDO7/SDMMC2_PWREN_M0/I2S1_SDI3_M1/VOP_BT656_D7_M1/GPIO3_D5_d |

WIFI_REG activer |

1.8V |

E/S BAS |

|

80 |

WIFI_WAKE_HOST_H_GPIO3_D4 |

CIF_D6/EBC_SDDO6/SDMMC2_DET_M0/I2S1_SDI2_M1/VOP_BT656_D6_M1/GPIO3_D4_d |

Hôte de réveil WIFI |

1.8V |

E/S BAS |

|

81 |

SDMMC2_CLK_M0 |

CIF_D5/EBC_SDDO5/SDMMC2_CLK_M0/I2S1_SDI1_M1/VOP_BT656_D5_M1/GPIO3_D3_d |

Horloge SDMMC2 |

1.8V |

E/S BAS |

|

82 |

SDMMC2_CMD_M0 |

CIF_D4/EBC_SDDO4/SDMMC2_CMD_M0/I2S1_SDI0_M1/VOP_BT656_D4_M1/GPIO3_D2_d |

Commande SDMMC2 |

1.8V |

E/S BAS |

|

83 |

SDMMC2_D3_M0 |

CIF_D3/EBC_SDDO3/SDMMC2_D3_M0/I2S1_SDO0_M1/VOP_BT656_D3_M1/GPIO3_D1_d |

Données SDMMC2 |

1.8V |

E/S BAS |

|

84 |

SDMMC2_D2_M0 |

CIF_D2/EBC_SDDO2/SDMMC2_D2_M0/I2S1_LRCK_TX_M1/VOP_BT656_D2_M1/GPIO3_D0_d |

Données SDMMC2 |

1.8V |

E/S BAS |

|

85 |

SDMMC2_D1_M0 |

CIF_D1/EBC_SDDO1/SDMMC2_D1_M0/I2S1_SCLK_TX_M1/VOP_BT656_D1_M1/GPIO3_C7_d |

Données SDMMC2 |

1.8V |

E/S BAS |

|

86 |

SDMMC2_D0_M0 |

CIF_D0/EBC_SDDO0/SDMMC2_D0_M0/I2S1_MCLK_M1/VOP_BT656_D0_M1/GPIO3_C6_d |

Données SDMMC2 |

1.8V |

E/S BAS |

|

87 |

GMAC1_INT/PMEB_GPIO3_A7 |

LCDC_D14/VOP_BT1120_D5/GMAC1_RXCLK_M0/SDMMC2_DET_M1/GPIO3_A7_d |

|

3.3V |

E/S BAS |

|

88 |

GMAC1_RSTN_GPIO3_B0 |

LCDC_D15/VOP_BT1120_D6/ETH1_REFCLKO_25M_M0/SDMMC2_PWREN_M1/GPIO3_B0_d |

|

3.3V |

E/S BAS |

|

89 |

GMAC1_MDIO_M1 |

IF_VSYNC/EBC_SDOE/GMAC1_MDIO_M1/I2S2_SCLK_TX_M1/GPIO4_B7_d |

Commande et données de gestion GMAC1 |

1.8V |

E/S BAS |

|

90 |

GMAC1_MDC_M1 |

CIF_HREF/EBC_SDLE/GMAC1_MDC_M1/UART1_RTSn_M1/I2S2_MCLK_M1/GPIO4_B6_d |

Horloge de gestion GMAC1 |

1.8V |

E/S BAS |

|

91 |

GMAC1_MCLKINOUT_M1 |

CIF_CLKIN/EBC_SDLK/GMAC1_MCLKINOUT_M1/UART1_CTSn_M1/I2S2_SCLK_RX_M1/GPIO4_C1_d |

Horloge externe GMAC1 |

1.8V |

E/S BAS |

|

92 |

ETH1_REFCLKO_25M_M1 |

I2C4_SCL_M0/EBC_GDOE/ETH1_REFCLKO_25M_M1/SPI3_CLK_M0/I2S2_SDO_M1/GPIO4_B3_d |

Sortie d'horloge ETH1 |

1.8V |

E/S BAS |

|

93 |

GMAC1_RXCLK_M1 |

CIF_D13/EBC_SDDO13/GMAC1_RXCLK_M1/UART7_RX_M2/PDM_SDI3_M1/GPIO4_A3_d |

Horloge de réception GMAC1 |

1.8V |

E/S BAS |

|

94 |

GMAC1_RXDV_CRS_M1 |

ISP_PRELIGHT_TRIG/EBC_SDCE3/GMAC1_RXDV_CRS_M1/I2S1_SDO2_M1/GPIO4_B1_d |

Signal valide de données GMAC1 RX |

1.8V |

E/S BAS |

|

95 |

GMAC1_RXD3_M1 |

CIF_D12/EBC_SDDO12/GMAC1_RXD3_M1/UART7_TX_M2/PDM_SDI2_M1/GPIO4_A2_d |

GMAC1 reçoit des données |

1.8V |

E/S BAS |

|

96 |

GMAC1_RXD2_M1 |

CIF_D11/EBC_SDDO11/GMAC1_RXD2_M1/PDM_SDI1_M1/GPIO4_A1_d |

GMAC1 reçoit des données |

1.8V |

E/S BAS |

|

97 |

GMAC1_RXD1_M1 |

CAM_CLKOUT1/EBC_SDCE2/GMAC1_RXD1_M1/SPI3_MISO_M0/I2S1_SDO1_M1/GPIO4_B0_d |

GMAC1 reçoit des données |

1.8V |

E/S BAS |

|

98 |

GMAC1_RXD0_M1 |

CAM_CLKOUT0/EBC_SDCE1/GMAC1_RXD0_M1/SPI3_CS1_M0/I2S1_LRCK_RX_M1/GPIO4_A7_d |

GMAC1 reçoit des données |

1.8V |

E/S BAS |

|

99 |

GMAC1_TXCLK_M1 |

CIF_D10/EBC_SDDO10/GMAC1_TXCLK_M1/PDM_CLK1_M1/GPIO4_A0_d |

Horloge de transmission GMAC1 |

1.8V |

E/S BAS |

|

100 |

GMAC1_TXEN_M1 |

ISP_FLASHTRIGOUT/EBC_SDCE0/GMAC1_TXEN_M1/SPI3_CS0_M0/I2S1_SCLK_RX_M1/GPIO4_A6_d |

Activation de la transmission GMAC1 |

1.8V |

E/S BAS |

|

101 |

GMAC1_TXD3_M1 |

CIF_D9/EBC_SDDO9/GMAC1_TXD3_M1/UART1_RX_M1/PDM_SDI0_M1/GPIO3_D7_d |

GMAC1 transmet des données |

1.8V |

E/S BAS |

|

102 |

GMAC1_TXD2_M1 |

CIF_D8/EBC_SDDO8/GMAC1_TXD2_M1/UART1_TX_M1/PDM_CLK0_M1/GPIO3_D6_d |

GMAC1 transmet des données |

1.8V |

E/S BAS |

|

103 |

GMAC1_TXD1_M1 |

CIF_D15/EBC_SDDO15/GMAC1_TXD1_M1/UART9_RX_M2/I2S2_LRCK_RX_M1/GPIO4_A5_d |

GMAC1 transmet des données |

1.8V |

E/S BAS |

|

104 |

GMAC1_TXD0_M1 |

CIF_D14/EBC_SDDO14/GMAC1_TXD0_M1/UART9_TX_M2/I2S2_LRCK_TX_M1/GPIO4_A4_d |

GMAC1 transmet des données |

1.8V |

E/S BAS |

|

105 |

TP_RST_L_GPIO0_B6 |

I2C2_SDA_M0/SPI0_MOSI_M0/PCIE20_PERSTn_M0/PWM2_M1/GPIO0_B6_u |

Réinitialisation de l'écran tactile |

3.3V |

E/S HAUT

|

|

106 |

TP_INT_L_GPIO0_B5 |

I2C2_SCL_M0/SPI0_CLK_M0/PCIE20_WAKEn_M0/PWM1_M1/GPIO0_B5_u |

Entrée de données d'interruption de l'écran tactile |

3.3V |

E/S HAUT |

|

107 |

I2C1_SDA_TP |

I2C1_SDA/CAN0_RX_M0/PCIE20_BUTTONRSTn/MCU_JTAG_TCK/GPIO0_B4_u |

Port série I2C 1 |

3.3V |

E/S HAUT |

|

108 |

I2C1_SCL_TP |

I2C1_SCL/CAN0_TX_M0/PCIE30X1_BUTTONRSTn/MCU_JTAG_TDO/GPIO0_B3_u |

Port série I2C 1 |

3.3V |

E/S HAUT |

|

109 |

I2C3_SCL_M0 |

I2C3_SCL_M0/UART3_TX_M0/CAN1_TX_M0/AUDIOPWM_LOUT_N/ACODEC_ADC_CLK/GPIO1_A1_u |

Port série I2C 3 |

3.3V |

E/S HAUT |

|

110 |

I2C3_SDA_M0 |

I2C3_SDA_M0/UART3_RX_M0/CAN1_RX_M0/AUDIOPWM_LOUT_P/ACODEC_ADC_DATA/GPIO1_A0_u |

Port série I2C 3 |

3.3V |

E/S HAUT |

|

111 |

I2C2_SCL_M1 |

I2C2_SCL_M1/EBC_SDSHR/CAN2_TX_M0/I2S1_SDO3_M1/GPIO4_B5_d |

Port série I2C 2 |

1.8V |

E/S BAS |

|

112 |

I2C2_SDA_M1 |

I2C2_SDA_M1/EBC_GDSP/CAN2_RX_M0/ISP_FLASH_TRIGIN/VOP_BT656_CLK_M1/GPIO4_B4_d |

Port série I2C 2 |

1.8V |

E/S BAS |

|

113 |

MIPI_CAM1_PDN_L_GPIO3_D3 |

LCDC_D1/VOP_BT656_D1_M0/SPI0_MOSI_M1/PCIE20_WAKEn_M1/I2S1_SCLK_TX_M2/GPIO2_D1_d |

Mise hors tension de la caméra 1 |

3.3V |

E/S BAS |

|

114 |

MIPI_CAM1_RST_L_GPIO3_D2 |

LCDC_D0/VOP_BT656_D0_M0/SPI0_MISO_M1/PCIE20_CLKREQn_M1/I2S1_MCLK_M2/GPIO2_D0_d |

Réinitialisation de la caméra 1 |

3.3V |

E/S BAS |

|

115 |

MIPI_CAM0_RST_L_GPIO3_D4 |

LCDC_D2/VOP_BT656_D2_M0/SPI0_CS0_M1/PCIE30X1_CLKREQn_M1/I2S1_LRCK_TX_M2/GPIO2_D2_d |

Réinitialisation de la caméra0 |

3.3V |

E/S BAS |

|

116 |

MIPI_CAM0_PDN_L_GPIO3_D5 |

LCDC_D3/VOP_BT656_D3_M0/SPI0_CLK_M1/PCIE30X1_WAKEn_M1/I2S1_SDI0_M2/GPIO2_D3_d |

Mise hors tension de la caméra0 |

3.3V |

E/S BAS |

|

117 |

USB2_HOST2_DM |

USB2_HOST2_DM |

USB2_HOST2_DM |

3.3V |

- |

|

118 |

USB2_HOST2_DP |

USB2_HOST2_DP |

USB2_HOST2_DP |

3.3V |

- |

|

119 |

USB2_HOST3_DM |

USB2_HOST3_DM |

USB2_HOST3_DM |

3.3V |

- |

|

120 |

USB2_HOST3_DP |

USB2_HOST3_DP |

USB2_HOST3_DP |

3.3V |

- |

|

121 |

REFCLK_OUT |

REFLK_OUT/GPIO0_A0_d |

Sortie d'horloge pour caméra |

3.3V |

E/S BAS |

|

122 |

CIF_CLKOUT |

CIF_CLKOUT/EBC_GDCLK/PWM11_IR_M1/GPIO4_C0_d |

Horloge CIF |

1.8V |

E/S BAS |

|

123 |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

MIPI_CSI_RX_D3P |

1.8V |

- |

|

124 |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

MIPI_CSI_RX_D3N |

1.8V |

- |

|

125 |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

MIPI_CSI_RX_D2P |

1.8V |

- |

|

126 |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

MIPI_CSI_RX_D2N |

1.8V |

- |

|

127 |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

MIPI_CSI_RX_CLK1P |

1.8V |

- |

|

128 |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

MIPI_CSI_RX_CLK1N |

1.8V |

- |

|

129 |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

MIPI_CSI_RX_CLK0P |

1.8V |

- |

|

130 |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

MIPI_CSI_RX_CLK0N |

1.8V |

- |

|

131 |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

MIPI_CSI_RX_D1P |

1.8V |

- |

|

132 |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

MIPI_CSI_RX_D1N |

1.8V |

- |

|

133 |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

MIPI_CSI_RX_D0P |

1.8V |

- |

|

134 |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

MIPI_CSI_RX_D0N |

1.8V |

- |

|

135 |

LCD1_PWREN_H_GPIO0_C5 |

PWM6/SPI0_MISO_M0/PCIE30X2_WAKEn_M0/GPIO0_C5_d |

Activation de l'alimentation LCD |

3.3V |

E/S BAS |

|

136 |

LCD1_BL_PWM5 |

PWM5/SPI0_CS1_M0/UART0_RTSn/GPIO0_C4_d |

Rétroéclairage LCD PWM |

3.3V |

E/S BAS |

|

137 |

LCD1_BL_PWM4 |

PWM4/VOP_PWM_M0/PCIE30X1_PERSTn_M0/MCU_JTAG_TRSTn/GPIO0_C3_d |

Rétroéclairage LCD PWM |

3.3V |

E/S BAS |

|

138 |

LCD0_PWREN_H_GPIO0_C7 |

HDMITX_CEC_M1/PWM0_M1/UART0_CTSn/GPIO0_C7_d |

Activation de l'alimentation LCD |

3.3V |

E/S BAS |

|

139 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3P |

1.8V |

- |

|

140 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D3N |

1.8V |

- |

|

141 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2P |

1.8V |

- |

|

142 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D2N |

1.8V |

- |

|

143 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKP |

1.8V |

- |

|

144 |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

MIPI_DSI_TX0_D3P/LVDS_TX0_CLKN |

1.8V |

- |

|

145 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1P |

1.8V |

- |

|

146 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D1N |

1.8V |

- |

|

147 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0P |

1.8V |

- |

|

148 |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

MIPI_DSI_TX0_D3P/LVDS_TX0_D0N |

1.8V |

- |

|

149 |

HDMI_TXCLKN_PORT |

HDMI_TX_CLKN |

HDMI_TX2CLKN_PORT et résistance série 2.2R |

1.8V |

- |

|

150 |

HDMI_TXCLKP_PORT |

HDMI_TX_CLKP |

HDMI_TXCLKP_PORT et résistance série 2.2R |

1.8V |

- |

|

151 |

HDMI_TX0N_PORT |

HDMI_TX_D0N |

HDMI_TX0N_PORT et résistance série 2.2R |

1.8V |

- |

|

152 |

HDMI_TX0P_PORT |

HDMI_TX_D0P |

HDMI_TX0P_PORT et résistance série 2.2R |

1.8V |

- |

|

153 |

HDMI_TX1N_PORT |

HDMI_TX_D1N |

HDMI_TX1N_PORT et résistance série 2.2R |

1.8V |

- |

|

154 |

HDMI_TX1P_PORT |

HDMI_TX_D1P |

HDMI_TX1P_PORT et résistance série 2.2R |

1.8V |

- |

|

155 |

HDMI_TX2N_PORT |

HDMI_TX_D2N |

HDMI_TX2N_PORT et résistance série 2.2R |

1.8V |

- |

|

156 |

HDMI_TX2P_PORT |

HDMI_TX_D2P |

HDMI_TX2P_PORT et résistance série 2.2R |

1.8V |

- |

|

157 |

HDMITX_SCL |

HDMITX_SCL/I2C5_SCL_M1/GPIO4_C7_u |

Port série I2C pour HDMI |

3.3V |

E/S HAUT |

|

158 |

HDMITC_SDA |

HDMITX_SDA/I2C5_SDA_M1/GPIO4_D0_u |

Port série I2C pour HDMI |

3.3V |

E/S HAUT |

|

159 |

HDMITX_CEC_M0 |

HDMITX_CEC_M0/SPI3_CS1_M1/GPIO4_D1_u |

HDMITX_CEC |

3.3V |

E/S HAUT |

|

160 |

HDMI_TX_HPDIN |

HDMI_TX_HPDIN |

Prise à chaud HDMI_TX |

1.8V |

- |

|

161 |

PCIE30X2_CLKREQN_M1 |

LCDC_D4/VOP_BT656_D4_M0/SPI2_CS1_M1/PCIE30X2_CLKREQn_M1/I2S1_SDI1_M2/GPIO2_D4_d |

PCIE30X2_CLKREQn |

3.3 |

E/S BAS |

|

162 |

PCIE30X2_WAKEN_M1 |

LCDC_D5/VOP_BT656_D5_M0/SPI2_CS0_M1/PCIE30X2_WAKEn_M1/I2S1_SDI2_M2/GPIO2_D5_d |

PCIE30X2_WAKEn |

3.3V |

E/S BAS |

|

163 |

PCIE30X2_PERSTN_M1 |

LCDC_D6/VOP_BT656_D6_M0/SPI2_MOSI_M1/PCIE30X2_PERSTn_M1/I2S1_SDI3_M2/GPIO2_D6_d |

Réinitialisation PCIE30X2 |

3.3V |

E/S BAS |

|

164 |

PCIE30X2_PRSNT_L_GPIO2_D7 |

LCDC_D7/VOP_BT656_D7_M0/SPI2_MISO_M1/UART8_TX_M1/I2S1_SDO0_M2/GPIO2_D7_d |

Hôte de réveil PCIE30X2 |

3.3V |

E/S BAS |

|

165 |

PCIE_PWREN_H_GPIO0_D4 |

GPIO0_D4_d |

Activation de l'alimentation PCIE |

1.8V |

E/S BAS |

|

166 |

PCIE30_RX1N |

PCIE30_RX1N |

PCIE30_RX1N |

1.8V |

- |

|

167 |

PCIE30_RX1P |

PCIE30_RX1P |

PCIE30_RX1P |

1.8V |

- |

|

168 |

PCIE30_RX0N |

PCIE30_RX0N |

PCIE30_RX0N |

1.8V |

- |

|

169 |

PCIE30_RX0P |

PCIE30_RX0P |

PCIE30_RX0P |

1.8V |

- |

|

170 |

PCIE30_TX1N |

PCIE30_TX1N |

PCIE30_TX1N |

1.8V |

- |

|

171 |

PCIE30_TX1P |

PCIE30_TX1P |

PCIE30_TX1P |

1.8V |

- |

|

172 |

PCIE30_TX0N |

PCIE30_TX0N |

PCIE30_TX0N |

1.8V |

- |

|

173 |

PCIE30_TX0P |

PCIE30_TX0P |

PCIE30_TX0P |

1.8V |

- |

|

174 |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

PCIE30_REFCLKN_IN |

1.8V |

- |

|

175 |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

PCIE30_REFCLKP_IN |

1.8V |

- |

|

176 |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

PCIE20_REFCLKN |

1.8V |

- |

|

177 |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

PCIE20_REFCLKP |

1.8V |

- |

|

178 |

SATA2_RXN |

PCIE20_RXN/SATA2_RXN/QSGMII_RXN_M1 |

SATA2_RXN |

1.8V |

- |

|

179 |

SATA2_RXP |

PCIE20_RXP/SATA2_RXP/QSGMII_RXP_M1 |

SATA2_RXP |

1.8V |

- |

|

180 |

SATA2_TXN |

PCIE20_TXN/SATA2_TXN/QSGMII_TXN_M1 |

SATA2_TXN |

1.8V |

- |

|

181 |

SATA2_TXP |

PCIE20_TXP/SATA2_TXP/QSGMII_TXP_M1 |

SATA2_TXP |

1.8V |

- |

|

182 |

SATA2_ACT_LED |

EDP_HPDIN_M0/SPDIF_TX_M2/SATA2_ACT_LED/PCIE30X2_PERSTn_M2/I2S3_LRCK_M1/GPIO4_C4_d |

SATA actif indique |

3.3V |

E/S BAS |

|

183 |

USB3_HOST1_SSTXP |

USB3_HOST1_SSTXP/SATA1_TXP/QSGMII_TXP_M0 |

USB3_HOST1_SSTXP |

1.8V |

- |

|

184 |

USB3_HOST1_SSTXN |

USB3_HOST1_SSTXN/SATA1_TXN/QSGMII_TXN_M0 |

USB3_HOST1_SSTXN |

1.8V |

- |

|

185 |

USB3_HOST1_SSRXP |

USB3_HOST1_SSRXP/SATA1_RXP/QSGMII_RXP_M0 |

USB3_HOST1_SSRXP |

1.8V |

- |

|

186 |

USB3_HOST1_SSRXN |

USB3_HOST1_SSRXN/SATA1_RXN/QSGMII_RXN_M0 |

USB3_HOST1_SSRXN |

1.8V |

- |

|

187 |

USB3_HOST1_DM |

USB3_HOST1_DM |

USB3_HOST1_DM |

3.3V |

- |

|

188 |

USB3_HOST1_DP |

USB3_HOST1_DP |

USB3_HOST1_DP |

3.3V |

- |

|

189 |

USB3_OTG0_SSTXP |

USB3_OTG0_SSTXP/SATA0_TXP |

USB3_OTG0_SSTXP |

1.8V |

- |

|

190 |

USB3_OTG0_SSTXN |

USB3_OTG0_SSTXN/SATA0_TXN |

USB3_OTG0_SSTXN |

1.8V |

- |

|

191 |

USB3_OTG0_SSRXP |

USB3_OTG0_SSRXP/SATA0_RXP |

USB3_OTG0_SSRXP |

1.8V |

- |

|

192 |

USB3_OTG0_SSRXN |

USB3_OTG0_SSRXN/SATA0_RXN |

USB3_OTG0_SSRXN |

1.8V |

- |

|

193 |

USB3_OTG0_DM |

USB3_OTG0_DM |

USB3_OTG0_DM |

3.3V |

- |

|

194 |

USB3_OTG0_DP |

USB3_OTG0_DP |

USB3_OTG0_DP |

3.3V |

- |

|

195 |

USB3_OTG0_ID |

USB3_OTG0_ID |

USB3_OTG0_ID |

3.3V |

- |

|

196 |

USB3_OTG0_VBUSDET |

USB3_OTG0_VBUSDET |

Détection USB3_OTG0_VBUS |

3.3V |

- |

|

197 |

USB_HOST_PWREN_H_GPIO0_A6 |

GPU_PWREN/SATA_CP_POD/PCIE30X2_CLKREQn_M0/GPIO0_A6_d |

Activation de l'alimentation de l'hôte USB |

3.3V |

E/S BAS |

|

198 |

USB_OTG_PWREN_H_GPIO0_A5 |

SDMMC0_PWREN/SATA_MP_SWITCH/PCIE20_CLKREQn_M0/GPIO0_A5_d |

Activation de l'alimentation USB OTG |

3.3V |

E/S BAS |

|

199 |

DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

MIPI_DSI_TX1_D3N/EDP_TX_D3N |

1.8V |

- |

|

200 |

DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

MIPI_DSI_TX1_D3P/EDP_TX_D3P |

1.8V |

- |

|

201 |

DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

MIPI_DSI_TX1_D2N/EDP_TX_D2N |

1.8V |

- |

|

202 |

DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

MIPI_DSI_TX1_D2P/EDP_TX_D2P |

1.8v |

- |

|

203 |

DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

MIPI_DSI_TX1_D1N/EDP_TX_D1N |

1.8V |

- |

|

204 |

DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

MIPI_DSI_TX1_D1P/EDP_TX_D1P |

1.8V |

- |

|

205 |

DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

MIPI_DSI_TX1_D0N/EDP_TX_D0N |

1.8V |

- |

|

206 |

DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

MIPI_DSI_TX1_D0P/EDP_TX_D0P |

1.8V |

- |

|

207 |

DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

MIPI_DSI_TX1_CLKN/EDP_TX_AUN |

1.8V |

- |

|

208 |

DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

MIPI_DSI_TX1_CLKP/EDP_TX_AUP |

1.8V |

- |

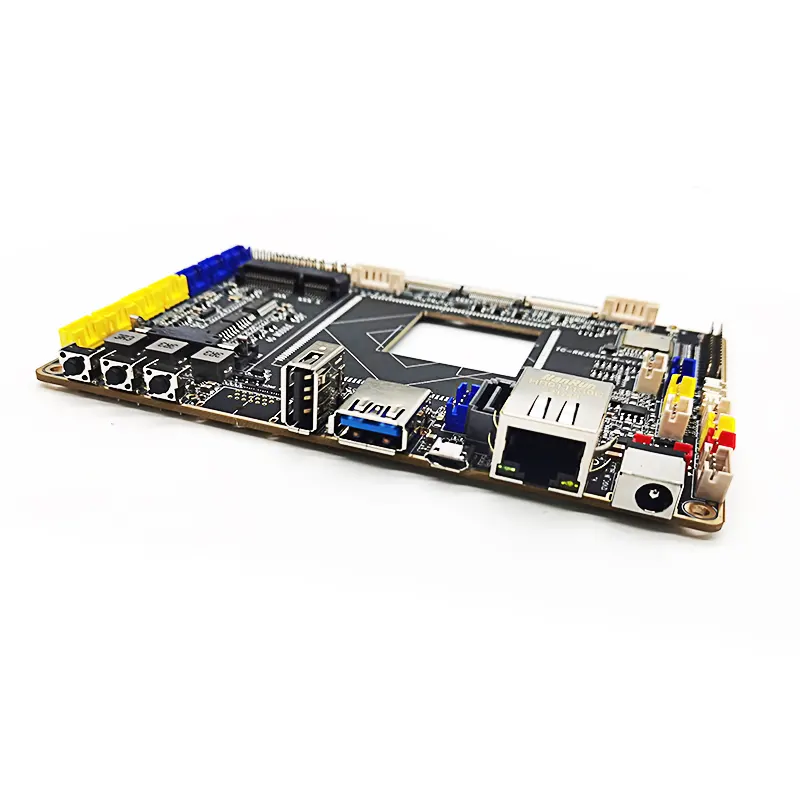

Chapitre 3. Conseil de développement

Taille

La taille est de 150 mm * 110 mm, 4 couches, épaisseur 1,6 mm.

Description des interfaces

|

Description des interfaces |

|

|

NON. |

Nom |

|

ã1ã |

Entrée cc 12 V/entrée 4 broches 2,54 mm 12 V |

|

ã2ã |

Emplacement pour carte SIM du module 4G |

|

ã3ã |

Fente pour carte TF |

|

ã4ã |

OTG USB |

|

ã5ã |

HÔTE USB3.0 |

|

ã6ã |

Données SATA |

|

ã7ã |

Sortie HDMI |

|

ã8ã |

LCD MIPI1 |

|

ã9ã |

LCD MIPI0 |

|

ã10ã |

Caméra MIPI |

|

ã11ã |

USB2.0 * 3 |

|

ã12ã |

USB2.0 TypeA |

|

ã13ã |

Wi-Fi/BT (AP6335) |

|

ã14ã |

RTC |

|

ã15ã |

ETH0 |

|

ã16ã |

ETH1 |

|

ã17ã |

Mettre à jour la clé |

|

ã18ã |

Touche de réinitialisation |

|

ã19ã |

Clé d'alimentation |

|

ã20ã |

Clés (4 broches 2,0 mm) |

|

ã21ã |

PEUT (3 broches 2,0 mm) |

|

ã22ã |

Uart TTL (4 broches 2,0 mm) |

|

ã23ã |

RS232 * 2 (4 broches 2,0 mm) |

|

ã24ã |

RS485 (4 broches 2,0 mm) |

|

ã25ã |

VENTILATEUR (2 broches 2,0 mm) |

|

ã26ã |

MIC (2 broches 2,0 mm) |

|

ã27ã |

HP (2 broches 2,0 mm) |

|

ã28ã |

SPK (2 broches 2,0 mm) |

|

ã29ã |

Sortie d'alimentation (4 broches 2,0 mm) |

|

ã30ã |

Débogage Uart (4 broches 2,0 mm) |

|

ã31ã |

GPIO (2*10 broches 2,0 mm) |

|

ã32ã |

Emplacement de module 4G (port PCIE) |

|

ã33ã |

SOM RK3568 |

La carte utilise une alimentation 12 V CC, qui se connecte par un connecteur d'entrée CC 12 V ou un connecteur d'entrée 4 broches 2,54 mm 12 V.

Les détails des autres interfaces peuvent se référer au diagramme schématique et à la disposition de la carte de développement.

Chapitre 4. Conception matérielle

Référence de conception

Prenez la carte de développement TC-RK3568 comme plate-forme matérielle, vous pouvez vous référer à la conception de l'alimentation, à la conception USB, à la conception du port PCIE, à la conception de l'affichage MIPI, à la conception audio, à la conception Ethernet, à la conception de la caméra, etc. Ceux-ci sont ouverts aux clients, peuvent se référer à notre conception de carte de support.

Chapitre 5. Conception de logiciels

La plate-forme de développement TC-RK3568 prend en charge Android11, Linux Buildroot, Ubuntu et Debian System OS, les codes sources sont ouverts. Vous pouvez lire les références telles que le manuel d'utilisation du système Thinkcore TC-RK3568.